模擬集成電路設(shè)計(jì)入門指南

模擬集成電路設(shè)計(jì)是電子工程領(lǐng)域的重要分支,它專注于設(shè)計(jì)用于處理連續(xù)信號(hào)的集成電路。與數(shù)字電路不同,模擬電路處理的是電壓和電流的連續(xù)變化,廣泛應(yīng)用于放大器、濾波器、電源管理和傳感器接口等場景。對(duì)于初學(xué)者而言,掌握模擬集成電路設(shè)計(jì)需要理解基礎(chǔ)理論、設(shè)計(jì)流程和常用工具。

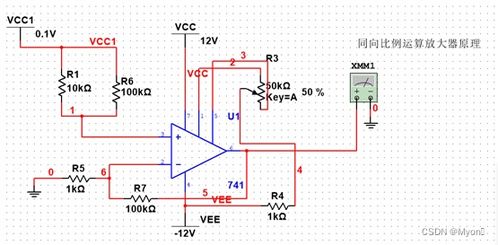

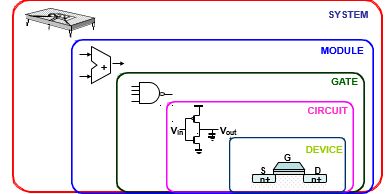

基礎(chǔ)知識(shí)是入門的關(guān)鍵。模擬電路設(shè)計(jì)涉及半導(dǎo)體物理、器件模型(如MOSFET和BJT)、電路分析(如基爾霍夫定律和小信號(hào)模型)以及頻率響應(yīng)等概念。初學(xué)者應(yīng)學(xué)習(xí)如何分析基本電路模塊,例如運(yùn)算放大器、電流鏡和差分對(duì),這些是復(fù)雜模擬系統(tǒng)的構(gòu)建塊。

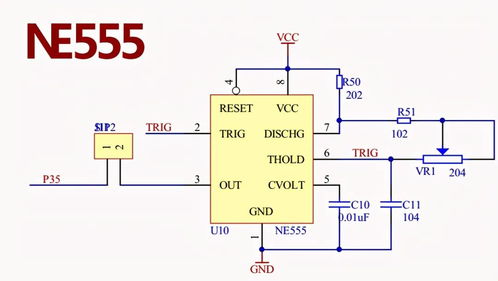

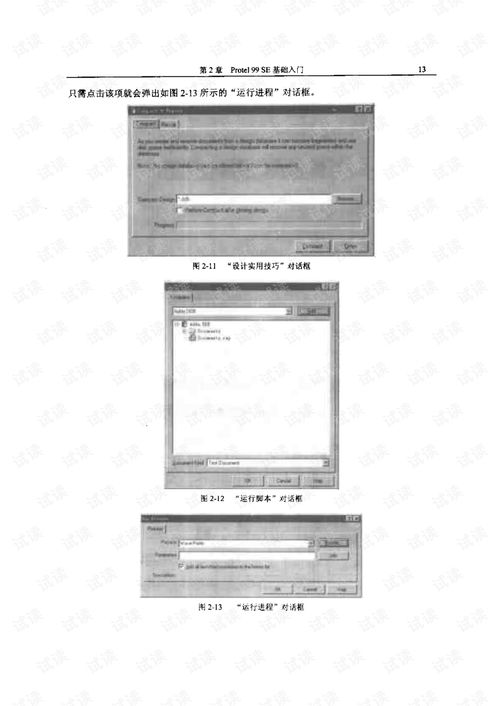

設(shè)計(jì)流程通常包括規(guī)格定義、電路拓?fù)溥x擇、仿真驗(yàn)證和版圖設(shè)計(jì)。在規(guī)格階段,需明確性能參數(shù)如增益、帶寬和功耗;然后,選擇適當(dāng)?shù)碾娐方Y(jié)構(gòu)并使用EDA工具(如Cadence或SPICE)進(jìn)行仿真,以優(yōu)化設(shè)計(jì)。版圖設(shè)計(jì)是物理實(shí)現(xiàn)的關(guān)鍵,涉及布局、布線和寄生效應(yīng)管理,確保芯片制造的可靠性。

實(shí)踐是提升技能的核心。初學(xué)者可以從簡單項(xiàng)目入手,如設(shè)計(jì)一個(gè)基本放大器或電壓基準(zhǔn)源,通過仿真和實(shí)際測試加深理解。同時(shí),閱讀經(jīng)典教材(如拉扎維的《模擬CMOS集成電路設(shè)計(jì)》)和參與在線課程能加速學(xué)習(xí)進(jìn)程。

模擬集成電路設(shè)計(jì)是一個(gè)需要耐心和細(xì)致實(shí)踐的領(lǐng)域。通過系統(tǒng)學(xué)習(xí)理論、掌握工具并不斷實(shí)驗(yàn),初學(xué)者可以逐步構(gòu)建起扎實(shí)的設(shè)計(jì)能力,為更高級(jí)的應(yīng)用奠定基礎(chǔ)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.xmx100.com.cn/product/33.html

更新時(shí)間:2026-03-01 02:14:51