集成電路設(shè)計(jì)制造中的EDA工具實(shí)用教程

集成電路(Integrated Circuit, IC)是現(xiàn)代信息技術(shù)的基石,其設(shè)計(jì)與制造是一個(gè)極其復(fù)雜且精密的過程。在這個(gè)過程中,電子設(shè)計(jì)自動(dòng)化(Electronic Design Automation, EDA)工具扮演著不可或缺的核心角色。本文旨在結(jié)合韓雁教授的學(xué)術(shù)理念與實(shí)踐經(jīng)驗(yàn),為讀者提供一份關(guān)于集成電路設(shè)計(jì)制造中EDA工具的實(shí)用入門指南。

一、EDA工具概述

EDA工具是一套軟件系統(tǒng)的集合,它貫穿于集成電路設(shè)計(jì)的全流程,從系統(tǒng)設(shè)計(jì)、邏輯設(shè)計(jì)、電路設(shè)計(jì)到物理設(shè)計(jì)(版圖設(shè)計(jì)),再到最終的制造數(shù)據(jù)生成與驗(yàn)證。其核心目標(biāo)是提高設(shè)計(jì)效率、保證設(shè)計(jì)正確性、優(yōu)化芯片性能并縮短產(chǎn)品上市時(shí)間。沒有EDA工具,動(dòng)輒包含數(shù)十億晶體管的高端芯片設(shè)計(jì)將無法實(shí)現(xiàn)。

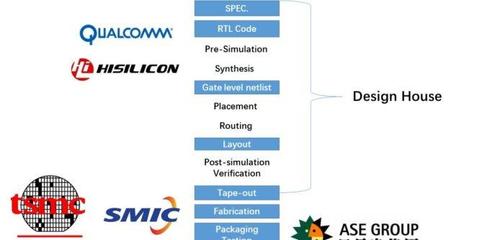

二、集成電路設(shè)計(jì)流程與對應(yīng)的EDA工具

典型的數(shù)字集成電路設(shè)計(jì)流程可分為以下幾個(gè)階段,每個(gè)階段都有其主導(dǎo)的EDA工具:

- 前端設(shè)計(jì)(邏輯設(shè)計(jì)):

- 系統(tǒng)級設(shè)計(jì)與驗(yàn)證:使用高級建模語言(如SystemC、SystemVerilog)和仿真工具(如Synopsys VCS、Cadence Xcelium)進(jìn)行算法建模和架構(gòu)探索。

- 寄存器傳輸級(RTL)設(shè)計(jì):使用硬件描述語言(HDL),主要是Verilog或VHDL,進(jìn)行功能描述。這是設(shè)計(jì)的核心輸入。

- 功能仿真與驗(yàn)證:對RTL代碼進(jìn)行仿真,驗(yàn)證其功能是否符合設(shè)計(jì)規(guī)范。Modelsim(現(xiàn)為Mentor Graphics/Siemens EDA產(chǎn)品)是經(jīng)典的仿真工具之一。

- 邏輯綜合:將RTL代碼轉(zhuǎn)換為基于特定工藝庫的門級網(wǎng)表。Synopsys的Design Compiler是該領(lǐng)域的行業(yè)標(biāo)準(zhǔn)工具。

- 形式驗(yàn)證:在綜合前后,使用數(shù)學(xué)方法驗(yàn)證設(shè)計(jì)在功能上是否等價(jià),確保轉(zhuǎn)換過程無錯(cuò)誤。Synopsys Formality是常用工具。

- 后端設(shè)計(jì)(物理設(shè)計(jì)):

- 布局規(guī)劃:規(guī)劃芯片的宏觀結(jié)構(gòu),確定核心模塊、存儲單元、I/O接口等的位置。

- 布局與布線:將綜合后的門級網(wǎng)表在硅片上實(shí)現(xiàn)具體的物理幾何圖形,并完成其間的互連。Cadence Innovus和Synopsys IC Compiler是主流工具。

- 時(shí)鐘樹綜合:構(gòu)建一個(gè)低偏差、低功耗的全局時(shí)鐘分布網(wǎng)絡(luò),確保所有時(shí)序單元能同步工作。

- 物理驗(yàn)證:檢查設(shè)計(jì)是否滿足制造工藝的所有物理和電氣規(guī)則,主要包括設(shè)計(jì)規(guī)則檢查(DRC)和版圖與電路圖一致性檢查(LVS)。Cadence Virtuoso和Synopsys IC Validator是常用平臺。

- 寄生參數(shù)提取與后仿真:從最終版圖中提取出電阻、電容等寄生參數(shù),并帶入仿真環(huán)境進(jìn)行帶寄生參數(shù)的時(shí)序與功能驗(yàn)證,確保芯片在真實(shí)物理?xiàng)l件下的性能。

三、實(shí)用學(xué)習(xí)路徑與建議(以韓雁教授的教學(xué)理念為參考)

對于初學(xué)者或?qū)W生而言,系統(tǒng)地掌握EDA工具應(yīng)遵循以下路徑:

- 夯實(shí)理論基礎(chǔ):深刻理解半導(dǎo)體物理、數(shù)字電路與系統(tǒng)、硬件描述語言(Verilog/VHDL)等基礎(chǔ)知識。這是有效使用EDA工具的前提。

- 建立流程觀念:首先要對從RTL到GDSII的完整設(shè)計(jì)流程有宏觀認(rèn)識,理解每個(gè)步驟的目標(biāo)、輸入和輸出。

- 從點(diǎn)工具入手:選擇一兩個(gè)關(guān)鍵工具進(jìn)行深度實(shí)踐。例如:

- 前端:熟練使用一種仿真工具(如ModelSim)進(jìn)行RTL仿真調(diào)試;掌握邏輯綜合的基本腳本編寫與約束設(shè)置。

- 后端:學(xué)習(xí)使用Virtuoso進(jìn)行簡單的模擬電路或標(biāo)準(zhǔn)單元版圖繪制,并運(yùn)行DRC/LVS。對于數(shù)字后端,可以從學(xué)習(xí)一個(gè)開源流程(如OpenLane)開始。

- 項(xiàng)目驅(qū)動(dòng)學(xué)習(xí):最好的學(xué)習(xí)方式是通過實(shí)際項(xiàng)目。可以從一個(gè)小型數(shù)字電路(如一個(gè)簡單的CPU內(nèi)核或通信編碼模塊)開始,嘗試完成從RTL編寫、功能仿真、邏輯綜合到布局布線(可使用大學(xué)計(jì)劃提供的免費(fèi)工藝庫)的全流程實(shí)踐。

- 關(guān)注設(shè)計(jì)與工藝的協(xié)同:理解EDA工具與工藝技術(shù)文件的緊密關(guān)系。工藝庫(.lib)、設(shè)計(jì)規(guī)則文件(.tf, .drf)等都是工具運(yùn)行的依據(jù)。

四、主流EDA廠商與工具生態(tài)

目前全球EDA市場主要由三家公司主導(dǎo),它們提供了幾乎全流程的工具鏈:

- Synopsys(新思科技):在邏輯綜合、靜態(tài)時(shí)序分析、IP核領(lǐng)域優(yōu)勢明顯。

- Cadence(楷登電子):在模擬/混合信號設(shè)計(jì)、數(shù)字后端布局布線、驗(yàn)證平臺方面實(shí)力雄厚。

- Siemens EDA(原Mentor Graphics):在形式驗(yàn)證、可測試性設(shè)計(jì)(DFT)、PCB設(shè)計(jì)等領(lǐng)域領(lǐng)先。

初學(xué)者可通過各公司提供的大學(xué)計(jì)劃獲取免費(fèi)或低成本的軟件授權(quán)和教學(xué)資料。

###

EDA工具是集成電路設(shè)計(jì)工程師的“畫筆”與“標(biāo)尺”。掌握它,不僅意味著學(xué)會操作軟件,更意味著深刻理解其背后的設(shè)計(jì)原理、約束條件和優(yōu)化目標(biāo)。以韓雁教授等業(yè)界學(xué)者所倡導(dǎo)的“理論與實(shí)踐緊密結(jié)合”的精神為指導(dǎo),通過系統(tǒng)的學(xué)習(xí)和持續(xù)的實(shí)踐,設(shè)計(jì)者才能將這些強(qiáng)大的工具轉(zhuǎn)化為實(shí)現(xiàn)創(chuàng)新芯片構(gòu)想的關(guān)鍵能力,最終在集成電路的微觀世界中描繪出宏偉的藍(lán)圖。

如若轉(zhuǎn)載,請注明出處:http://m.xmx100.com.cn/product/70.html

更新時(shí)間:2026-03-01 15:57:51